Article

# A Parallel FPGA Implementation of the CCSDS-123 Compression Algorithm

Milica Orlandić 1\*D, Johan Fjeldtvedt 1D and Tor Arne Johansen 2D

- Department of Electronic Systems, Norwegian University of Science and Technology, Norway

- <sup>2</sup> Centre for Autonomous Marine Operations and Systems (NTNU-AMOS), Department of Engineering Cybernetics, Norwegian University of Science and Technology, Norway

- \* Correspondence: milica.orlandic@ntnu.no

Version December 19, 2018 submitted to Journal Not Specified

- Abstract: Satellite onboard processing for hyperspectral imaging applications is characterized by

- large data sets, limited processing resources and limited bandwidth of communication links. The

- 3 CCSDS-123 algorithm is a specialized compression standard assembled for space-related applications.

- In this paper, a parallel FPGA implementation of CCSDS-123 compression algorithm is presented.

- 5 The proposed design can compress any number of samples in parallel allowed by resource and

- 6 I/O bandwidth constraints. The CCSDS-123 processing core has been placed on Zynq-7035 SoC

- and verified against the existing reference software. The estimated power use scales approximately

- linearly with the number of samples processed in parallel. Finally, the proposed implementation

- outperforms the state-of-the-art implementations in terms of both throughput and power.

- Keywords: CCSDS-123, compression, parallel implementation, Field programmable gate arrays

(FPGA), hyperspectral imaging, Real-time processing

# 2 1. Introduction

13

19

In recent years, the space development has moved towards small-satellite (SmallSat) missions which are characterized by capable low-cost platforms with introduced budget and schedule flexibility. Space-related applications such as synthetic aperture radar (SAR), multi- and hyper-spectral imaging (HSI) require critical data processing to be performed onboard in order to preserve transmission bandwidth. In this respect, the compression algorithms are commonly used as a final step in onboard processing pipelines to reduce memory access and limit data transfer to Earth. To fulfill real-time data processing requirement, hybrid processing systems with reconfigurable hardware have become the standard choice.

Hyper- and multi-spectral imaging have been both widely used in remote sensing Earth observation missions in the recent few decades. Unlike multispectral sensors, such as Landsat, MSG and MODIS [1], with a fairly limited number of discrete spectral bands, hyperspectral sensors record a very large number of narrow spectral bands. Airborne hyperspectral sensors such as Compact Airborne Spectrographic Imager (CASI), Airborne Visible/InfraRed Imaging Spectrometer (AVIRIS) [2], Infrared Atmospheric Sounding Interferometer (IASI) [3] and the Hyperspectral Imager for the Coastal Ocean (HICO) [4,5] have provided an expansion of hyperspectral research in the number of applications such as environmental monitoring, coastal ecosystems, geology and land cover. A hyperspectral imager has recently been deployed on an intellegent nano-satellite [6], where a key feature is intensive onboard data processing including operations such as comparisons of images in subsequent orbits. However, a mission with HSI payload to fulfill its objectives, in addition to smart onboard processing, requires compression for downlink of the acquired data.

37

38

42

43

48

53

55

58

60

63

71

72

73

78

79

The Consultative Committee for Space Data Systems (CCSDS) has developed image compression algorithms [7–10] specifically designed for space data systems. In particular, the CCSDS-123 compression standard [9,10] is an efficient prediction-based algorithm characterized by low complexity and, thus, is suitable for real-time hardware implementation. In fact, in the recent years a number of FPGA implementations of the CCSDS-123 standard are presented in the literature [11–17]. Keymeulen et al [11] propose an on-the-fly implementation in BIP sample ordering. In the implementation proposed by Santos et al [12], the focus is on low complexity and low memory footprint. The chosen BSQ sample ordering requires only one weight vector and one accumulator to be stored. However, in the presented approach, repeated computation of local differences decreases the input bandwidth efficiency. This approach requires either the non-sequential memory access pattern with potentially reduction of streaming efficiency, or that the data is arranged in memory in the desired streaming order. The serial CCSDS-123 implementation with BIP ordering proposed by Theodorou et al [13] relies on external memory to buffer samples coming from the image sensor such that the current, N and NE neighboring samples are streamed in parallel reducing greatly on-chip memory requirements. The downside is, however, lack of support for on-the-fly compression. Báscones et al [14] propose an implementation with BIP sample ordering characterized by the ability to perform compression without relying on external memory. This is achieved by queuing incoming samples in internal FIFOs, resulting in linear dependence of memory usage with respect to the product of width and depth of a HSI cube.

A parallel CCSDS-123 implementation proposed by Báscones et al [15] consists of a number of instances of the CCSDS-123 core. Other than sharing local differences, the cores operate independently by processing samples from a fixed subset of bands. If the number of bands is not divisible by number of parallel cores, some cores are stalled during processing of the last samples of each pixel. Another limitation of the implementation is that the packing operation of the resulting code words from each core is performed in serial manner creating a significant throughput bottleneck for large number of parallel cores. The paper suggests, however, that the serial packing circuit can be clocked faster.

In this paper, an efficient parallel FPGA implementation of the CCSDS-123 compression algorithm is proposed. A number of samples processed in parallel by the proposed core is only constrained by the logic resources of the chosen technology, whereas the high throughput is achieved by the use of a number of optimization techniques for data routing between parallel processing pipelines.

The paper is structured as follows: Section 2 presents an overview of the CCSDS-123 standard. The proposed parallel hardware implementation is described in Section 3. The influence of the number of pipelines and chosen architectural solutions on the logic utilization, timing and power are analyzed in Section 4. Finally, the conclusions are given in Section 5.

## 2. Background

The CCSDS-123 standard for lossless data compressors [10] is applicable to 3D HSI data cubes produced by multispectral and hyperspectral imagers and sounders, where a 3D HSI data cube is a three-dimensional array  $(N_x, N_y, N_z)$ . The standard supports Band Interleaved by Pixel (BIP), Band Interleaved by Line (BIL) and Band Sequential (BSQ) orderings for scanning the HSI coordinates.

The integer samples of HSI cube are labeled as  $s_{z,y,x}$  or  $s_z(t)$  where  $t=y\cdot N_x+x$ . The sample  $s_{z,y,x}$  is predicted by computation of a local sum  $\sigma_{z,y,x}$  of nearby predicted samples  $(s_{z,y,x-1},s_{z,y-1,x-1},s_{z,y-1,x-1},s_{z,y-1,x+1})$  at positions (N,NW,W,NE) with respect to sample  $s_{z,y,x}$ . The reduced prediction mode computes central local differences  $d^k$  for previously processed bands  $k=0,\ldots,P$  as  $d^k=4\cdot (s_{z-k,y,x})-\sigma_{z-k,y,x}$ , whereas full prediction mode includes also the directional differences  $[d^N,d^{NW},d^W]$  in the band z. The created differences are then stored in the local difference vector  $U_z(t)$ .

The computation of the rounded scaled predicted sample value  $\tilde{s}_r(t)$  includes the dot product operation of weight vector  $W_z(t)$  and local difference vector  $U_z(t)$  and shifting operation of local sum  $\sigma_z(t)$  by parameter  $\Omega$  which is defined as bit precision of the weight elements. The scaled predicted sample value  $\tilde{s}_z(t)$  is a version of  $\tilde{s}_r(t)$  constraint to the range  $[-2^{D-1}, 2^{D-1}]$  for signed integers,

where D is a dynamic range of HSI samples. The weights are dynamically updated based on the prediction error  $e_z = 2s_z(t) - \tilde{s}_z(t)$  by the weight update factor  $\Delta W_z(t)$  which depends on a number of user-defined parameters controlling convergence speed and determining the rate at which the predictor adapts to the image statistics. The scaled predicted sample value  $\tilde{s}_z(t)$  is re-normalized to the range of the input sample (D-bit quantity) resulting in  $\hat{s}_z(t)$ . Finally, the residual mapping converts the signed predicted residual  $\Delta_z(t) = s_z(t) - \hat{s}_z(t)$  to a D-bit unsigned integer mapped prediction residual  $\delta_z(t)$ .

In the sample-adaptive encoding, code words are generated based on the average value of the input residuals in each band. The encoder updates an accumulator  $\Sigma_z(t)$  by storing recent sample values and then divides the result by the counter  $\Gamma(t)$  which tracks the number of processed samples. A code word generator computes quotient and residual pair,  $(u_z, r_z)$  from the division  $\frac{\delta_z(t)}{2^{k_z(t)}}$ , where the parameter  $k_z(t)$  is defined as the largest non-negative integer satisfying an inequality expression depending on relations between the accumulator  $\Sigma_z(t)$  and the counter  $\Gamma(t)$ .

## ₀₅ 3. Implementation

87

91

100

103

104

105

106

108

109

110

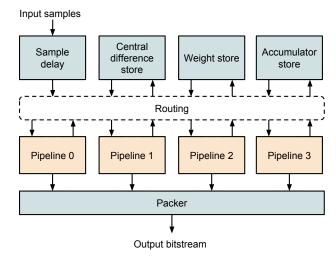

The proposed parallel implementation of the CCSDS-123 algorithm builds upon the sequential implementation presented in [18]. It contains  $N_p$  pipelines for concurrent sample processing and shared resources for storing intermediate data. The block diagram of the proposed implementation for  $N_p = 4$  is shown in Figure 1.

**Figure 1.** Overview of the parallel CCSDS-123 implementation for  $N_p = 4$

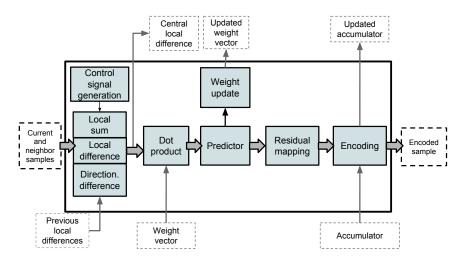

A number of data samples are streamed into the sample delay module in each clock cycle. A pipeline contains a chain of modules performing the local sum and difference computation, prediction, residual mapping and sample adaptive encoding as illustrated in Figure 2. The predicted data computed in central local differences, the updated weight vector elements and accumulator values in sample adaptive encoding are stored in the central difference store, the weight store and accumulator store modules, respectively, which are shared between the pipelines.

The data packages streamed into the CCSDS-123 core contain  $N_p$  samples. A lane is defined as a position of samples in the input package. Figure 3a and 3b show the sample placement grids for  $N_p = 4$  lanes in the first 10 clock cycles for the number of bands is  $N_z = 8$  and  $N_z = 9$ , respectively. When the number of bands is divisible by the number of pipelines i.e.  $N_z \mod N_p = 0$ , lane i contains a fixed subset of bands for each pixel so that the sample from band z is always streamed in the lane  $i = z \mod N_p$ . For  $N_z$  not divisible by  $N_p$ , samples from the same band are no longer confined to a specific lane. Instead, samples shift between lanes. After streaming the last sample in a pixel, the input stream can be stalled so that the first sample of the next pixel is in lane i = 0. In this manner, a fixed subset of samples is processed by each pipeline similarly to the case when  $N_z$  is divisible by

119

120

122

Figure 2. Overview of pipeline architecture

$N_p$ . The downside of the introduced stalling is reduced throughput and additional logic. To avoid stalling, an interleaved pipeline approach is proposed. In this approach, samples from the same bands are processed in different pipelines, requiring from pipelines to share additional information besides local differences. For instance, a sample arriving to the sample delay module in lane i=0 is also sent to pipeline 2 as the neighbor of a sample arriving to lane i=2. Furthermore, vector  $W_0(1)$  is produced by pipeline 0 when processing  $s_0(0)$ , but it is then also used by pipeline 1 when processing  $s_0(1)$ . The advantage of the interleaved approach is a generic implementation with maximized throughput and independent of the parameters  $N_z$  and  $N_p$ .

|                    | Lane               | es                 |                    |                |                    | Lane               | es                 |                    |                |

|--------------------|--------------------|--------------------|--------------------|----------------|--------------------|--------------------|--------------------|--------------------|----------------|

| 3                  | 2                  | 1                  | 0                  | Clock<br>Cycle | 3                  | 2                  | 1                  | 0                  | Clock<br>Cycle |

| s <sub>3</sub> (0) | s <sub>2</sub> (0) | s <sub>1</sub> (0) | s <sub>0</sub> (0) |                | s <sub>3</sub> (0) | s <sub>2</sub> (0) | s <sub>1</sub> (0) | s <sub>0</sub> (0) |                |

| s <sub>7</sub> (0) | s <sub>6</sub> (0) | s <sub>5</sub> (0) | s <sub>4</sub> (0) |                | s <sub>7</sub> (0) | s <sub>6</sub> (0) | s <sub>5</sub> (0) | s <sub>4</sub> (0) |                |

| s <sub>3</sub> (1) | s <sub>2</sub> (1) | s <sub>1</sub> (1) | s <sub>0</sub> (1) |                | s <sub>2</sub> (1) | s <sub>1</sub> (1) | s <sub>0</sub> (1) | s <sub>8</sub> (0) |                |

| s <sub>7</sub> (1) | s <sub>6</sub> (1) | s <sub>5</sub> (1) | s <sub>4</sub> (1) |                | s <sub>6</sub> (1) | s <sub>5</sub> (1) | s <sub>4</sub> (1) | s <sub>3</sub> (1) |                |

| s <sub>3</sub> (2) | s <sub>2</sub> (2) | s <sub>1</sub> (2) | s <sub>0</sub> (2) |                | s <sub>1</sub> (2) | s <sub>0</sub> (2) | s <sub>8</sub> (1) | s <sub>7</sub> (1) | 1              |

| s <sub>7</sub> (2) | s <sub>6</sub> (2) | s <sub>5</sub> (2) | s <sub>4</sub> (2) |                | s <sub>5</sub> (2) | s <sub>4</sub> (2) | s <sub>3</sub> (2) | s <sub>2</sub> (2) |                |

| s <sub>3</sub> (3) | s <sub>2</sub> (3) | s <sub>1</sub> (3) | s <sub>0</sub> (3) |                | s <sub>0</sub> (3) | s <sub>8</sub> (2) | s <sub>7</sub> (2) | s <sub>6</sub> (2) |                |

| s <sub>7</sub> (3) | s <sub>6</sub> (3) | s <sub>5</sub> (3) | s <sub>4</sub> (3) |                | s <sub>4</sub> (3) | s <sub>3</sub> (3) | s <sub>2</sub> (3) | s <sub>1</sub> (3) | 1              |

| s <sub>3</sub> (4) | s <sub>2</sub> (4) | s <sub>1</sub> (4) | s <sub>0</sub> (4) |                | s <sub>8</sub> (3) | s <sub>7</sub> (3) | s <sub>6</sub> (3) | s <sub>5</sub> (3) | 1              |

| s <sub>7</sub> (4) | s <sub>6</sub> (4) | s <sub>5</sub> (4) | s <sub>4</sub> (4) |                | s <sub>3</sub> (4) | s <sub>2</sub> (4) | s <sub>1</sub> (4) | s <sub>0</sub> (4) |                |

|                    |                    | (a)                |                    |                |                    |                    | (b)                |                    | -              |

**Figure 3.** Sample placement timing diagram, (a)  $N_z = 8$ ,  $N_p = 4$ , (b)  $N_z = 9$ ,  $N_p = 4$

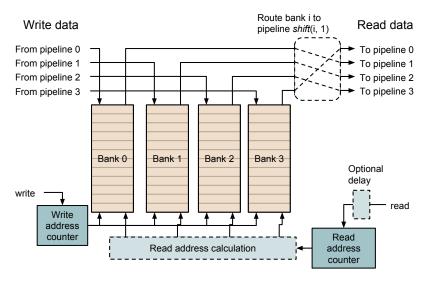

The data shifting is introduced for moving data from different lanes to corresponding processing pipelines. If a current sample is in lane i, then the sample with distance n from the current sample is in lane  $(i+n) \mod N_p$ . The distance between neighboring samples  $s_z(t)$  in lane i and  $s_z(t+\Delta t)$  is given as  $N_z\Delta t$ , where the lane of sample  $s_z(t+\Delta t)$  is computed as:

$$shift(i, \Delta t) = (i + N_z \Delta t) \mod N_v. \tag{1}$$

In Figure 3b, sample  $s_0(5)$  is streamed in the lane which is computed as shift(3, 2) = 0 based on the distance from sample  $s_0(3)$  from lane i=3. Due to the data shifting, the number of clock cycles

between samples within the same band is not constant. The number of clock cycles between two samples is equivalent to the number of rows between them in the grid. In the edge case, when sample  $s_z(t)$  is in the left-most lane, sample  $s_{z+1}(t)$  is streamed in the right-most lane of the next row. The time delay between  $s_{z+1}(t)$  and  $s_z(t)$  in lane i is computed as follows:

$$delay(i, \Delta t) = \left\lfloor \frac{i + N_z \Delta t}{N_p} \right\rfloor. \tag{2}$$

#### 3.1. Pipeline

123

124

127

128

131

132

A pipeline contains a chain of modules built upon the previous work on serial implementation of the CCSDS-123 algorithm [18], where to accommodate parallel processing, a number of modifications are introduced such as setting FIFO depth and RAM size to  $z/N_z$  instead of z.

#### 3.2. Sample delay

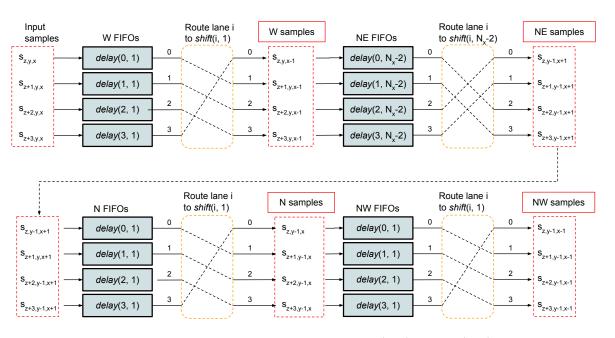

The sample delay module delays incoming samples so that the current sample and the previously predicted neighboring samples are available at its output. The proposed parallel implementation of sample delay module is shown in Figure 4. For each lane i, there is a set of FIFOs with the depth determined by the delay(i,  $\Delta t$ ) function. The outputs of FIFOs are then shifted according to the shift(i,  $\Delta t$ ) function, so that the delayed samples are used as neighbors in (W, NW, N, NE) positions with respect to the sample which is currently processed by the pipeline. The performed sample delay operation described by the use of the streaming grid (lanes, clock cycles) is presented in Figure 5. In the example, W neighbors ( $s_1(1)$ ,  $s_0(1)$ ,  $s_8(0)$ ,  $s_7(0)$ ) of samples ( $s_1(2)$ ,  $s_0(2)$ ,  $s_8(1)$ ,  $s_7(1)$ ) are obtained by delay and shift operations.

**Figure 4.** Sample delay processing chain described by delay(i,  $\Delta t$ ) and shift(i,  $\Delta t$ ) functions

#### 3.3. Local differences

137

138

141

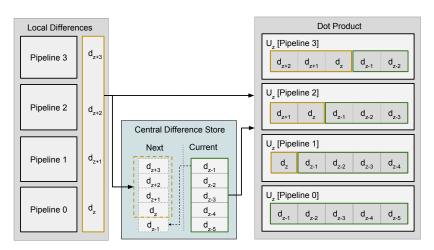

The computed local differences are stored in the central difference store since there is a need to share differences between the pipelines. The local difference vectors  $U_z$  for each pipeline are assembled as a combination of local differences from lower indexed pipelines and from the central difference store. The pipeline with the lowest index contains P differences only from the central difference store. An example of local differences routing between pipelines and to/from the central difference store for

| Incor              | Incoming stream From W FIFO |                    |                    |                |       |                    |                    |                      |   | From \             | W FIFC             | shifted            |                    | Beat |

|--------------------|-----------------------------|--------------------|--------------------|----------------|-------|--------------------|--------------------|----------------------|---|--------------------|--------------------|--------------------|--------------------|------|

| 3                  | 2                           | 1                  | 0                  | 3              | 3     | 2                  | 1                  | 0                    |   | 3                  | 2                  | 1                  | 0                  |      |

| s <sub>3</sub> (0) | s <sub>2</sub> (0)          | s <sub>1</sub> (0) | s <sub>0</sub> (0) |                | 1     |                    |                    | lay(0,1)<br>lay(1,1) |   |                    |                    | shift((            | ) 1)               |      |

| s <sub>7</sub> (0) | s <sub>6</sub> (0)          | s <sub>5</sub> (0) | s <sub>4</sub> (0) | С              | lelay | (3,1)              |                    | lay(2,1)             | 5 |                    |                    | Silit              |                    |      |

| s <sub>2</sub> (1) | s <sub>1</sub> (1)          | s <sub>0</sub> (1) | s <sub>8</sub> (0) |                |       | s <sub>2</sub> (0) | s <sub>1</sub> (0) | s <sub>0</sub> (0)   |   | s <sub>2</sub> (0) | s <sub>1</sub> (0) | s <sub>0</sub> (0) | shift(             | 3,1) |

| s <sub>6</sub> (1) | s <sub>5</sub> (1)          | s <sub>4</sub> (1) | s <sub>3</sub> (1) | s <sub>3</sub> | (0)   | s <sub>6</sub> (0) | s <sub>5</sub> (0) | s <sub>4</sub> (0)   |   | s <sub>6</sub> (0) | s <sub>5</sub> (0) | s <sub>4</sub> (0) | s <sub>3</sub> (0) |      |

| s <sub>1</sub> (2) | s <sub>0</sub> (2)          | s <sub>8</sub> (1) | s <sub>7</sub> (1) | s <sub>7</sub> | (0)   | s <sub>1</sub> (1) | s <sub>0</sub> (1) | s <sub>8</sub> (0)   |   | s <sub>1</sub> (1) | s <sub>0</sub> (1) | s <sub>8</sub> (0) | s <sub>7</sub> (0) |      |

| s <sub>5</sub> (2) | s <sub>4</sub> (2)          | s <sub>3</sub> (2) | s <sub>2</sub> (2) | s <sub>2</sub> | (1)   | s <sub>5</sub> (1) | s <sub>4</sub> (1) | s <sub>3</sub> (1)   |   | s <sub>5</sub> (1) | s <sub>4</sub> (1) | s <sub>3</sub> (1) | s <sub>2</sub> (1) |      |

| s <sub>0</sub> (3) | s <sub>8</sub> (2)          | s <sub>7</sub> (2) | s <sub>6</sub> (2) | s <sub>6</sub> | (1)   | s <sub>0</sub> (2) | s <sub>8</sub> (1) | s <sub>7</sub> (1)   |   | s <sub>0</sub> (2) | s <sub>8</sub> (1) | s <sub>7</sub> (1) | s <sub>6</sub> (1) |      |

**Figure 5.** Sample delay operation for obtaining W neighbor samples for  $N_p = 4$  and  $N_z = 9$

$N_p=4$  and P=5 is illustrated in Figure 6. Pipelines 0-3 produce local differences  $d_z(t)$  to  $d_{z+3}(t)$  for input samples  $s_z(t)$  to  $s_{z+3}(t)$ , respectively. Since each pipeline requires P previous local differences, pipeline 3 requires differences [ $d_{z+2}(t)$ ,  $d_{z+1}(t)$ ,  $d_z(t)$ ,  $d_{z-1}(t)$ ,  $d_{z-2}(t)$ ] where the differences [ $d_{z+2}(t)$ ,  $d_{z+1}(t)$ ,  $d_z(t)$ ] are produced by pipelines [ $d_{z+2}(t)$ ] in the current clock cycle and the other two elements [ $d_{z-1}(t)$ ,  $d_{z-2}(t)$ ] are fetched from the central difference store. After using  $d_z(t)$  differences from central difference store to create  $d_z(t)$  vectors, the differences from the bands in the range [ $d_z(t)$ ] are kept in the store to be used in the next clock cycle.

**Figure 6.** Routing of central differences between pipelines for  $N_p = 4$  and P = 5

When z < P, it is required to use only z previous local differences and no local differences remaining from the previous pixel. In the serial implementation, the contents of the difference store is set to zero when  $z = N_z - 1$ . For the parallel implementation, since previous local differences are used directly from the pipelines, the differences are masked based on the z coordinate. In this manner, the local differences with index  $i \le z$  are included in the local difference vector and elements with index i > z are set to zero.

# 3.4. Weights and accumulators

150

151

154

155

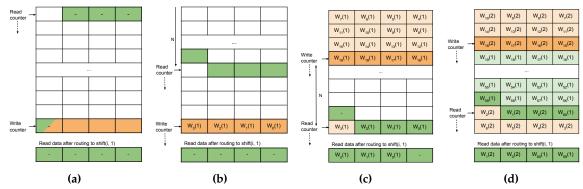

Weights and accumulators are stored in two instances of the same module, *shared store*, with different element sizes of stored vectors. Figure 7 shows the shared store implementation with  $N_p$  block RAMs of depth  $M = \lceil N_z/N_p \rceil$ . A read counter  $rd\_cnt$  and a write counter  $wr\_cnt$  are used for computation of the read and write addresses in each bank. The counters are initialized as  $rd\_cnt(i) = 0$

and  $wr\_cnt(i) = delay(0,1)$ . The write counter is used directly as the write address  $w\_addr(i)$ , whereas the read address  $r\_addr(i)$  for bank i is computed as follows:

$$r\_addr(i) = \begin{cases} rd\_cnt, & i + N_z \mod N_p < N_p \\ (rd\_cnt - 1) \mod M, & i + N_z \mod N_p \ge N_p, \end{cases}$$

(3)

creating the initial distance between the read and write addresses equal to delay(i, 1).

Figure 7. Implementation of the shared store module

Behaviour of the weight shared store for parameters  $N_z=61$ , M=16 and  $N_p=4$  is presented in Figure 8. The initial state after reset in Figure 8a shows that  $rd\_cnt$  is initialized to 0 and  $wr\_cnt$  is set to delay(0,1)=15. For lanes 0-2, the read addresses are equal to the counter value  $(rd\_cnt=0)$ , whereas for lane 3 the read address is 15 based on the condition  $(3+61 \mod 4) \ge 4$ . However, the data read from weight shared store for the first pixel are not used since the standard defines no prediction for the first pixel. Figure 8b shows the write operation of the first weight samples of pixel 1 at the address of the weight store pointed to by  $wr\_cnt$ . At this time stamp, counter  $rd\_cnt$  is N positions from its initial position, where the delay N corresponds to a number of pipeline stages from the weight reading operation to the end of the weight update operation. The delay N is equal to 8+S, where parameter S is the number of pipeline stages in the dot product. In Figure 8c, the read counter is set to position M-1, the  $r_{addr}$  are computed as [M-2, M-1, M-1, M-1] and the first weights  $[-, W_0(1), W_1(1), W_2(1)]$  are read simultaneously with samples  $[s_{60}(0), s_0(1), s_1(1), s_2(1)]$  at the input of the compression core. Figure 8d shows the state of weight shared store after 15 cycles when samples  $[s_{59}(1), s_{60}(1), s_{0}(2), s_1(2)]$  arrive at the input.

**Figure 8.** States of weight shared store for  $N_z = 61$  and  $N_p = 4$

157

158

159

160

161

164

165

166

169

## 3.5. Packing of variable length words

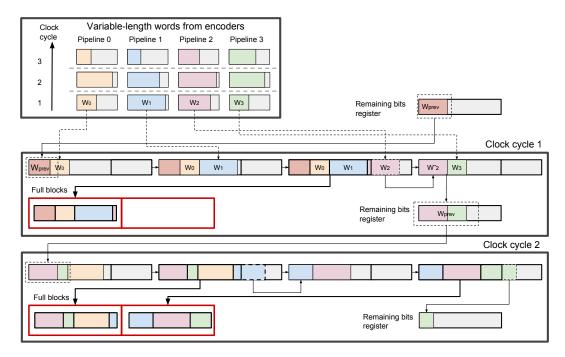

The last stage includes packing of the variable-length encoded words  $W_0, \ldots, W_{N_p-1}$  with respective lengths  $L_0, \ldots L_{N_p-1}$  from  $N_p$  pipelines into fixed-size blocks. The packing operation for  $N_p=4$  is illustrated in Figure 9. The packing process starts by shifting the word  $W_0$  from the first pipeline by the number of bits from the previous cycle,  $L_{prev}$ . After that, word  $W_0$  is concatenated to the bits remaining from the previous cycle,  $W_{prev}$ . In general, shifting of the word  $W_i$  by  $L_{prev}+L_0+\cdots+L_{i-1}$  positions is followed by concatenation of  $W_i$  to the chain  $W_{prev}W_0\ldots W_{i-1}$ . It is observed that the number of shifts depends heavily on  $N_p$  and maximum length  $U_{max}+D$  of each word. On the other side, the standard defines the fixed-size output blocks of size B which is extracted each time the sum of the words' lengths exceeds B. The block extraction limits the maximum word chain length to B-1 regardless of  $N_p$  or maximum world length. Therefore, the number of bits left after block extraction and the number of extracted blocks are introduced. The number of bits left after block extraction  $s_i$  is computed as follows:

$$s_i = \Sigma L_i \mod B, \tag{4}$$

where

$$\Sigma L_i = L_{prev} + \sum_{j=0}^{i-1} L_j. \tag{5}$$

The extraction count  $e_i$ , indicating the number of blocks to extract, is defined as:

$$e_i = \left| \frac{\Sigma L_i}{B} \right| . \tag{6}$$

If  $e_i$  is non-zero, the number of accumulated bits  $\sum L_i$  is greater than B. For  $U_{max} + D > B$ , the extraction count  $e_i$  is larger than 1. Otherwise,  $e_i$  is a flag indicating whether a block is created.

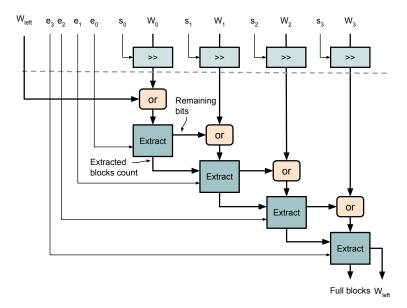

Figure 9. Operation of the variable length word packer

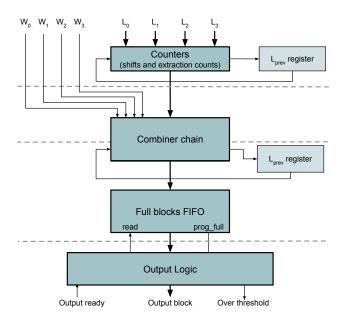

The implementation of packer module is presented in Figure 10. In the first stage, computation of  $s_i$  and  $e_i$  parameters is performed for input word  $W_i$ . In the second and third stage, a combiner chain combines input words using computed  $s_i$  and  $e_i$  as shown in Figure 11. The shifting operation for each

Figure 10. Implementation of variable length word packer

Figure 11. Implementation of combiner chain

180

181

185

186

190

191

192

word is performed in parallel by using  $s_i$  to select among shifted versions of  $W_i$  from a multiplexer. The last pipeline stage concatenates shifted words and extracts full blocks based on extraction count  $e_i$ . The produced full blocks are added to the chain of complete blocks, the count of full blocks is updated and the remaining bits  $W_{\text{prev}}$  are stored into a register to be combined in the next cycle. Finally, the last flag is set when the remaining bits are output as a separate block. After combiner chain, a chain of full blocks, its length and the last flag are pushed into an output FIFO. To output blocks sequentially, there is a need to buffer the blocks sent from the combiner. The data word width of the FIFO is determined by the maximum number of blocks  $N_{max}$  produced in one clock cycle given as:

$$N_{max} = \left| \frac{B - 1 + N_p(U_{max} + D)}{B} \right| + 1, \tag{7}$$

where (B-1) is the maximum number of leftover bits from the previous cycle,  $N_p(U_{max}+D)$  is the maximum word length produced in one clock cycle and factor 1 accounts for the last block when the last flag is set. If the average bit rate of the encoded samples is higher than the output bus width, there is risk for FIFO to become full. Thus, it is required to stall the data streaming into the core before the overflow occurs by de-asserting ready signal at the input. This is done by setting a threshold  $N_{th}$  to the number of data words in the FIFO. In this manner, it is ensured that all encoded samples, which are streamed in from the cycle when de-assertion of ready signal happens, are stored. The threshold  $N_{th}$  is equal to S+15 which corresponds to the total number of pipeline stages from the core input to the FIFO . In the on-the-fly processing, stalling of the input stream is not possible and the choice of FIFO depth is dependant on the image statistics and speed of predictor's ability to adapt.

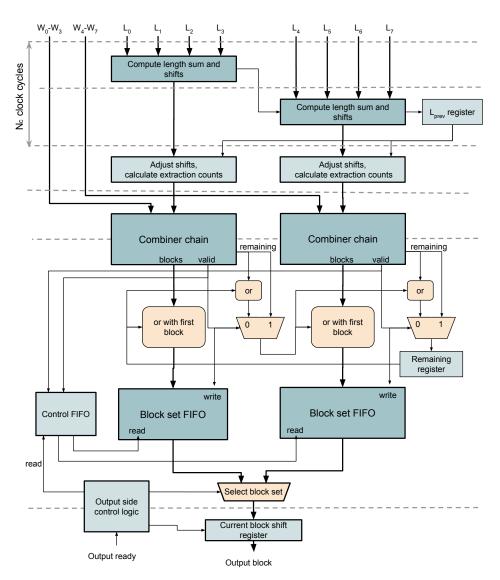

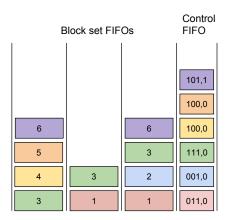

The proposed serial packing of incoming words in combinatorial logic is feasible for  $N_p < 6$ . For larger  $N_p$  values, the critical path in the initial pipeline stage does not meet timing requirements due to the dependence of sum of word lengths  $L_i$  on  $N_p$ . For this reason, a modified version of the packer module is presented in Figure 12. The modified packer distributes the incoming words across several combiner chains operating in parallel. Large critical paths are then avoided by displacing each combiner chain by one clock cycle. The generic parameter  $N_{per\_chain}$  is introduced to define the number of words per combiner chain where  $1 \le N_{per\_chain} \le N_p$ . The number of combiner chains  $N_c$  is computed as:

$$N_c = \lceil N_p / N_{per\_chain} \rceil. \tag{8}$$

The parameters  $s_i$  and  $e_i$  are computed sequentially for each combiner chain across  $N_c$  clock cycles as shown in Figure 12. Since this operation takes more than one clock cycle,  $L_{prev}$  is not available when computation starts. Therefore, the partial sum of word lengths are computed first as follows:

$$\Sigma \bar{L}_i = \sum_{j=0}^{i-1} L_j,\tag{9}$$

whereas the complete length  $\Sigma L_i = \bar{\Sigma} \bar{L}_i + L_{prev}$  is computed in the  $N_c$ -th clock cycle. After this, parameters  $s_i$ ,  $e_i$  and  $L_{prev}$  are computed. Large critical paths can be created due to existing data dependence between combiner chains. To avoid this, large delay registers for the left-most chains are used to keep the full blocks from each chain synchronized with the last chain  $N_c - 1$ . The proposed solution is that each combiner chain shifts its input words by  $L_{prev}$  without concatenating it with the remaining bits. Instead, the concatenation with remaining bits is done at the output of each combiner chain. The outputs of each combiner chain are a block set and a length of the produced block set which is sent to a block set FIFO. The output logic controls the streaming of created blocks and tracks which FIFO contains the packed blocks for that particular set of words. In particular, the control FIFO monitors which block set FIFOs contain valid data. For each block set pushed to the block FIFOs, a new word is pushed to the control FIFO with a *block set mask* and the last flag, where the bits in block

Figure 12. Implementation of improved variable length word packer

set mask correspond to one of the combiner chains. In Figure 13, block set mask '101.1' for  $N_c = 3$  indicates that valid block sets are from combiner chains 0 and 2 and last flag is high.

Figure 13. Memory organization for block set FIFOs

#### 4. Results

197

198

199

200

203

204

206

The proposed parallel architecture of the CCSDS-123 algorithm is described by the VHDL language, and the Vivado tool is used for synthesis, implementation, power estimation, testing and verification on a PicoZed board with a Zynq-7035 FPGA. The implementation supports BIP sample ordering and both on-the-fly and offline processing. In addition, the implementation is tested against the reference software Emporda [19] and it is fully compliant with the standard allowing user-defined parameter selection.

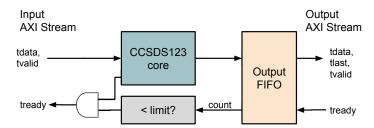

The proposed core implementation is tested as a part of a larger system supported by AXI bus [20]. Since the internal stalling of output stream is not supported by the core, it is necessary to buffer the output data in a FIFO as shown in Figure 14. Data streaming into the core is stopped when the number of words in FIFO is larger than a certain limit. The FIFO capacity limit  $N_{\text{limit}}$  is determined based on the assumption that each pipeline stage has valid data and each data word has the maximum length of  $U_{max} + D$  as follows:

$$N_{\text{limit}} = \text{FIFO capacity} - \left\lceil \frac{N_{\text{stages}}(U_{max} + D)}{B} \right\rceil.$$

(10)

The size of the FIFO can vary as long as it is larger than this limit and it is a trade-off between area usage and frequency of output stalling.

Figure 14. CCSDS-123 IP module

#### 4.1. Utilization results

Table 1 shows resource utilization for the proposed implementation for a variety of different hyperspectral and multispectral image sensors. The main factor affecting the area utilization results is

213

214

215

219

220

224

225

226

frame size  $N_x \cdot N_z$  which determines the amount of memory for storing delayed samples, weights and accumulators.

**Table 1.** Resource utilization for compressing HSI images from different sensors for  $N_p = 4$

| Model     | D  | $N_x$ | $N_y$ | $N_z$ | LUTs  | Regs  | RAM |

|-----------|----|-------|-------|-------|-------|-------|-----|

| SFSI      | 12 | 496   | 140   | 240   | 9416  | 8730  | 46  |

| MSG       | 10 | 3712  | 3712  | 11    | 7984  | 8133  | 16  |

| MODIS     | 12 | 1354  | 2030  | 17    | 8859  | 8682  | 12  |

| M3-Target | 12 | 640   | 2843  | 260   | 10824 | 8827  | 64  |

| M3-Global | 12 | 320   | 28283 | 386   | 11351 | 9086  | 48  |

| Landsat   | 8  | 1024  | 1024  | 8     | 6583  | 7410  | 7   |

| Hyperion  | 12 | 256   | 3242  | 242   | 9640  | 8888  | 28  |

| Crism-FRT | 12 | 640   | 510   | 545   | 12882 | 9313  | 130 |

| Crism-HRL | 12 | 320   | 480   | 545   | 12646 | 9130  | 68  |

| Crism-MSP | 12 | 64    | 2700  | 74    | 8803  | 8843  | 6   |

| CASI      | 12 | 405   | 2852  | 72    | 8922  | 8960  | 16  |

| AVIRIS    | 16 | 614   | 512   | 224   | 12033 | 10696 | 71  |

| AIRS      | 14 | 90    | 135   | 1501  | 12191 | 8569  | 68  |

| IASI      | 12 | 66    | 60    | 8461  | -     | -     | -   |

| HICO      | 16 | 512   | 2000  | 128   | 11589 | 10661 | 35  |

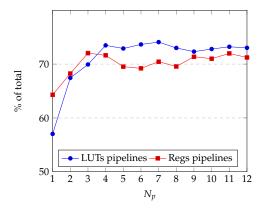

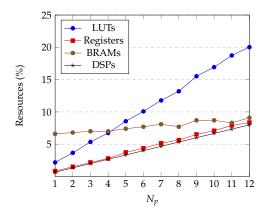

The used resources in terms of LUTs, registers and block RAM have been elaborated in more details for core configuration set to process data cubes of the HICO size [4]. Initially, the number of block RAMs varied considerably for different number of pipelines. In particular, weight store and sample delay block RAM utilization varied depending on  $N_p$ . This happens due to the synthesis tool which extends depth of an array to the closest power of 2, and by that increases significantly used block RAM resources. To avoid this, LUT elements are used as Distributed RAMs instead of block RAMs. Since one LUT element in 7-series FPGAs [21] can be configured as a  $32 \times 1$  bit dual port RAM, LUTs are used as RAM for storing weights, accumulators and in the one-pixel delay FIFOs, whereas block RAMs are used in NE FIFO module. The LUT utilization increases then linearly with  $N_x \cdot N_z$ . Regarding register utilization, each lane has its own memory element with read data registers and the register utilization in these modules scales linearly with  $N_p$ . The resources in terms of LUTs, registers and block RAMs used for the total design and the main components are presented in Table 2 and Table 3, respectively. It shows that the packer module is the largest contributor in logic utilization among shared modules. It is due to the fact that as  $N_p$  grows, the size of combiner chains for  $N_p \leq 4$ and the number of combiner chains for  $N_p > 4$  also increase. With the larger number of combiner chains, the number of block sets to select in the output logic also increases, requiring larger multiplexers for selection. Figure 15 shows that the resource utilization for a pipeline chain for  $N_p \ge 4$  stabilizes at 72% of total resources, whereas the ratio of used and available resources for the complete core grows linearly with  $N_p$  as presented in Figure 16. This means that the choice of  $N_p$  for the selected set of compression parameters and image size are constrained by available LUT resources.

|       |          |                 | LUT            | 'S              |        |       |

|-------|----------|-----------------|----------------|-----------------|--------|-------|

| $N_p$ | Pipeline | Sample<br>store | Accum<br>store | Weight<br>store | Packer | Total |

| 1     | 2137     | 468             | 112            | 504             | 526    | 3747  |

| 2     | 4247     | 672             | 128            | 366             | 884    | 6297  |

| 3     | 6435     | 866             | 196            | 566             | 1139   | 9202  |

| 4     | 8499     | 856             | 180            | 366             | 1665   | 11566 |

| 5     | 10723    | 1029            | 230            | 464             | 2263   | 14709 |

| 6     | 12765    | 1226            | 272            | 555             | 2513   | 17331 |

| 7     | 15005    | 1458            | 317            | 647             | 2826   | 20253 |

| 8     | 16550    | 1802            | 350            | 731             | 3238   | 22671 |

| 9     | 19297    | 2042            | 397            | 815             | 4131   | 26682 |

| 10    | 21191    | 1886            | 440            | 923             | 4668   | 29108 |

| 11    | 23584    | 2186            | 416            | 1014            | 5008   | 32208 |

| 12    | 25136    | 2268            | 454            | 1112            | 5455   | 34425 |

**Table 2.** LUT utilization in various stages for different  $N_p$

**Table 3.** Memory element utilization in various stages for different  $N_p$

|       |          |                | Regis         | sters          |        |       | В              | lock RAM | [     |

|-------|----------|----------------|---------------|----------------|--------|-------|----------------|----------|-------|

| $N_p$ | Pipeline | Samp.<br>store | Acc.<br>store | Weig.<br>store | Packer | Total | Samp.<br>store | Packer   | Total |

| 1     | 1856     | 156            | 36            | 152            | 687    | 2887  | 32             | 1        | 33    |

| 2     | 3532     | 238            | 56            | 280            | 1069   | 5175  | 32             | 2        | 34    |

| 3     | 5394     | 351            | 78            | 410            | 1255   | 7488  | 33             | 2        | 35    |

| 4     | 6869     | 440            | 98            | 546            | 1636   | 9589  | 32             | 3        | 35    |

| 5     | 8921     | 540            | 120           | 670            | 2579   | 12830 | 32.5           | 4.5      | 37    |

| 6     | 10424    | 648            | 142           | 814            | 3033   | 15061 | 33             | 5.5      | 38.5  |

| 7     | 12460    | 756            | 164           | 951            | 3358   | 17689 | 35             | 5.5      | 40.5  |

| 8     | 13455    | 808            | 184           | 1085           | 3810   | 19342 | 32             | 6.5      | 38.5  |

| 9     | 15994    | 909            | 206           | 1209           | 4094   | 22412 | 36             | 7.5      | 43.5  |

| 10    | 17311    | 1000           | 228           | 1332           | 4507   | 24378 | 35             | 8.5      | 43.5  |

| 11    | 19546    | 1100           | 250           | 1476           | 4784   | 27156 | 33             | 8.5      | 41.5  |

| 12    | 20479    | 1200           | 272           | 1611           | 5189   | 28751 | 36             | 9.5      | 45.5  |

Figure 15. Resource utilization by pipeline logic with respect to the available resources

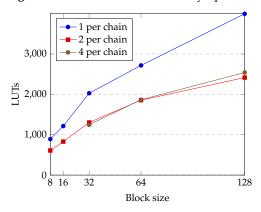

The LUT utilization in the packer module is analyzed in terms of a number of words per chain  $N_{per\_chain}$  and block sizes B and results are presented in Figure 17. It is observed that regardless of  $N_{per\_chain}$ , the block size is the main factor which greatly affects area utilization.

Figure 16. Resource utilization on Zynq Z-7035

**Figure 17.** LUT utilization in packer module for various *B* and  $N_{per\_chain}$ ,  $N_p = 4$

## 4.2. Timing

236

237

238

239

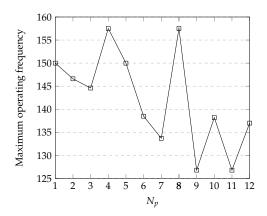

The maximum operating frequency of the proposed implementation for different  $N_p$  is shown in Figure 18. It is shown that the operating frequency depends on  $N_p$  with a downward trend and varies in the range 126-157 MHz. The critical path is in the output logic which produces the last flag signal obtained as a logically sum of the last signals from the control modules in each of the pipelines.

Figure 18. Maximum operating frequency for different number of pipelines

#### 4.3. Power estimation

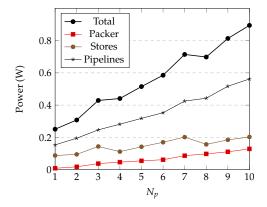

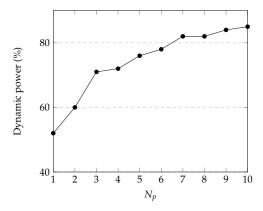

The power estimation has been performed in Xilinx Vivado on the post implementation design in combination with data in post-implementation functional simulation. Figure 19 shows that power usage increases linearly with  $N_p$  in all modules for  $1 \le N_p \le 8$ . Static power consumption of 0.125W is

247

248

249

255

256

257

261

262

mainly due to leakage in the memories in the stores, whereas dynamic power grows with respect to  $N_p$  as presented in Figure 20. The estimates for stores refer to the power sum in the weight, accumulator, sample and local difference stores. The linear increase is due to the added logic for each pipeline and to increasing complexity of the packer module. Fluctuations appear in the power contribution of the stores when  $N_p$  is power of 2 since inference of block RAMs in the NE FIFO of the sample delay module is the most effective when the depth of FIFO is a power of two. For  $N_x = 512$  and  $N_z = 128$  of HICO data, the depth of FIFO, computed as  $N_x N_z / N_p$ , is a power of two when  $N_p$  is also a power of two.

**Figure 19.** Power estimates for different  $N_p$

Figure 20. Dynamic power as percentage of total power usage

#### 4.4. Comparison with state-of-the-art implementations

The comparison of the proposed parallel implementation of CCSDS-123 algorithm with recent sequential [11–14,16,17] and parallel [15] FPGA implementations with regards to maximum frequency, the throughput performance and power is presented in Table 4. Sensor maximum data rates, representing real-time sensor throughput requirements, for AVIRIS NG and HICO imagers are also given. The implementations with BIP ordering have a roughly similar architecture but with large performance differences. In the implementation proposed by Santos et al [12], the chosen sample ordering requires that local differences are recomputed when needed. As a consequence, each sample is read 2(P+1) times and the input bandwidth efficiency is decreased. This approach requires either the non-sequential memory access pattern with potentially reduction of streaming efficiency, or that the arrangement of the data samples in memory follows the irregular streaming order, occupying 2(P+1) as much storage. The implementation SHyLoC [16] supports all three sample orderings, where a different architecture is suggested for each ordering. The implementation by Bascones et al [14] achieves throughput lower than 50 Msamples/s on Virtex-7 suggesting less than one sample compressed per clock cycle.

The proposed parallel implementation builds up on the previous work [18] which proposes a sequential implementation with throughput of 2350 Mb/s. In comparison with the state of the art, the parallel implementation achieves superior compression performance such as data rates of 9984 Mb/s and 12000 Mb/s for  $N_p = 4$  and  $N_p = 5$ , respectively. The ability to achieve high throughput for the images with the number of spectral bands  $N_z$ , which is not an integer multiple of  $N_p$ , and to pack any number of variable length words into fixed-size words in each clock cycle are the greatest improvements. The throughput is maximized by performing shift and delay operations to reorder weights, accumulators and delayed samples so that samples from different pixels are compressed concurrently.

| Implementation                | Order | P  | D  | Platform    | f <sub>max</sub><br>[MHz] | Throughput [MSa/s] | Throughput [Mb/s] | Power<br>[mW] |

|-------------------------------|-------|----|----|-------------|---------------------------|--------------------|-------------------|---------------|

| UAB Emporda [19]              | All   | 15 | 16 | (i-7 7500U) | -                         | 4.928 [14]         | 78                | -             |

| AVIRIS-NG [2]                 | -     | -  | 16 | Sensor Max. | -                         | 1.92               | 30.72             | -             |

| HICO [4]                      | -     | -  | 16 | Sensor Max. | -                         | 4.78               | 76.5              | -             |

| Keymeulen et al [11]          | BIP   | 3  | 13 | Virtex-5    | 40                        | 40                 | 520               | -             |

| HyLoC, Santos et al [12]      | BSQ   | 3  | 16 | Virtex-4    | 134                       | 11.2               | 179               | 1488          |

| Theodorou et al [13]          | BIP   | 3  | 16 | Virtex-5    | 110                       | 110                | 1790              | -             |

| Bascones et al [14]           | BIP   | 15 | 16 | Virtex-7    | 50                        | 47.6               | 760               | 450           |

| Bascones et al [15] - $C = 7$ | BIP   | 15 | 16 | Virtex-7    | -                         | 219.4              | 3510.4            | 5300          |

| SHyLoC, Santos et al [16]     | All   | 15 | 16 | Virtex5     | 140                       | 140                | 2240              | -             |

| Tsigkanos et al [17]          | BIP   | 3  | 16 | Virtex-5    | 213                       | 213                | 3300              | 4720          |

| Fjeldtvedt et al [18]         | BIP   | 15 | 16 | Zynq-7000   | 147                       | 147                | 2350              | 295           |

| Proposed work - $N_p = 4$     | BIP   | 15 | 16 | Zynq-7000   | 157                       | 624                | 9984              | 440           |

| Proposed work - $N_p' = 5$    | BIP   | 15 | 16 | Zynq-7000   | 150                       | 750                | 12000             | 515           |

Table 4. Performance comparison of CCSDS-123 implementations

#### 5. Conclusion

279

280

281

282

291

267

270

271

272

In this paper, the proposed parallel FPGA implementation of CCSDS-123 compression algorithm significantly outperforms the state-of-the-art designs in terms of throughput and power. In addition, operation of packing variable-length words is done fully in parallel implying that  $N_p$  samples can be compressed per clock cycle and the pipelines are fully utilized by performing shifting and delaying operations. The estimated power use scales linearly with the number of input samples. In conclusion, the proposed core can compress any number of samples in parallel provided that resource and I/O bandwidth constraints are obeyed.

Author Contributions: conceptualization, M.O. and J.F.; methodology, J.F.; validation, J.F., M.O. and T.A.J.; investigation, J.F.; writing—original draft preparation, M.O.; writing—review and editing, M.O., J.F. and T.A.J.; visualization, M.O.; supervision, M.O. and T.A.J.; project administration, T.A.J.; funding acquisition, T.A.J.

Acknowledgments: This work was supported by the Research Council of Norway (RCN) through the MASSIVE project, grant number 270959, and the AMOS project, grant number 223254, as well as by the Norwegian Space Center.

Conflicts of Interest: The authors declare no conflict of interest.

# References

- NASA. Moderate Resolution Imaging Spectroradiometer (MODIS). https://modis.gsfc.nasa.gov/. accessed on 12 November 2018.

- 294 2. NASA. Airborne Visible InfraRed Imaging Spectrometer (AVIRIS). https://aviris.jpl.nasa.gov/. accessed on 12 November 2018.

- <sup>296</sup> 3. Aires, F.; Chédin, A.; Scott, N.A.; Rossow, W.B. A regularized neural net approach for retrieval of atmospheric and surface temperatures with the IASI instrument. *Journal of Applied Meteorology* **2002**, 41, 144–159.

- Naval Research Laboratory. Hyperspectral Imager for the Coastal Ocean (HICO). http://hico.coas. oregonstate.edu/. accessed on 12 November 2018.

- 5. Corson, M.R.; Korwan, D.R.; Lucke, R.L.; Snyder, W.A.; Davis, C.O. The hyperspectral imager for the coastal ocean (HICO) on the international space station. Geoscience and Remote Sensing Symposium, 2008. IGARSS 2008. IEEE International. IEEE, 2008, Vol. 4, pp. IV–101.

- Soukup, M.; Gailis, J.; Fantin, D.; Jochemsen, A.; Aas, C.; Baeck, P.; Benhadj, I.; Livens, S.; Delauré, B.;

Menenti, M.; others. HyperScout: Onboard Processing of Hyperspectral Imaging Data on a Nanosatellite.

Proc. 4S conference, 2016.

- Consultative Committee for Space Data Systems. Lossless Multispectral and Hyperspectral Image

Compression CCSDS 121.0-B-1. Technical report, 2012.

- Consultative Committee for Space Data Systems. Lossless Multispectral and Hyperspectral Image

Compression CCSDS 122.0-B-1. Technical report, 2005.

- Gonsultative Committee for Space Data Systems. Lossless Multispectral and Hyperspectral Image

Compression CCSDS 123.0-B-1. Technical report, 2015.

- 313 10. Multispectral, L.; Standard, H.I.C. CCSDS 123.0-B-1. Blue Book 2012.

- Keymeulen, D.; Aranki, N.; Bakhshi, A.; Luong, H.; Sarture, C.; Dolman, D. Airborne demonstration of

FPGA implementation of Fast Lossless hyperspectral data compression system. Adaptive Hardware and

Systems (AHS), 2014 NASA/ESA Conference on. IEEE, 2014, pp. 278–284.

- Santos, L.; Berrojo, L.; Moreno, J.; López, J.F.; Sarmiento, R. Multispectral and hyperspectral lossless

compressor for space applications (HyLoC): A low-complexity FPGA implementation of the CCSDS 123

standard. IEEE Journal of Selected Topics in Applied Earth Observations and Remote Sensing 2016, 9, 757–770.

- Theodorou, G.; Kranitis, N.; Tsigkanos, A.; Paschalis, A. High Performance CCSDS 123.0-B-1 Multispectral

& Hyperspectral Image Compression Implementation on a Space-Grade SRAM FPGA. Proceedings of the

5th International Workshop on On-Board Payload Data Compression, Frascati, Italy, 2016, pp. 28–29.

- Báscones, D.; González, C.; Mozos, D. FPGA Implementation of the CCSDS 1.2.3 Standard for Real-Time

Hyperspectral Lossless Compression. *IEEE Journal of Selected Topics in Applied Earth Observations and Remote Sensing* 2017.

- Báscones, D.; González, C.; Mozos, D. Parallel Implementation of the CCSDS 1.2. 3 Standard for Hyperspectral Lossless Compression. *Remote Sensing* **2017**, *9*, 973.

- University of Las Palmas de Gran Canaria. SHyLoC IP Core. http://www.esa.int/Our\_Activities/Space\_ Engineering\_Technology/Microelectronics/SHyLoC\_IP\_Core. accessed on 12 November 2018.

- Tsigkanos, A.; Kranitis, N.; Theodorou, G.A.; Paschalis, A. 3.3 Gbps CCSDS 123.0-B-1 Multispectral Whyperspectral Image Compression Hardware Accelerator on a Space-Grade SRAM FPGA. *IEEE Transactions on Emerging Topics in Computing* **2018**.

- Fjeldtvedt, J.; Orlandić, M.; Johansen, T.A. An Efficient Real-Time FPGA Implementation of the CCSDS-123

Compression Standard for Hyperspectral Images. *IEEE Journal of Selected Topics in Applied Earth Observations* and Remote Sensing 2018, 11, 3841–3852. doi:10.1109/JSTARS.2018.2869697.

- 336 19. GICI group, Universitat Autonoma de Barcelona. Emporda Software. http://www.gici.uab.es. accessed on 12 November 2018.

- 20. ARM. AMBA AXI and ACE Protocol Specification. Technical report, 2011.

- 21. Xilinx. 7 Series FPGAs Configurable Logic Block User Guide. Technical report, 2016.

- Sample Availability: Samples of the compounds ..... are available from the authors.

- © 2018 by the authors. Submitted to *Journal Not Specified* for possible open access publication under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).